みなさん、こんにちは。

パワーデバイス設計課の中松です。今回はAQG-324規格のAnnex SiCで規格化されているQL-10 DRB試験(Dynamic Reverse Bias)についてお話ししようと思います。

※AQG-324規格とは、欧州の組織ECPEのワーキンググループによって車載向けパワーモジュール評価に関して策定された規格です。SiCデバイスはSiデバイスと比較して高速でスイッチングが可能なため、より動的なストレスが印加されることになります。そのため、SiCデバイスを高速にオンオフさせ、高dV/dtを印加してパッケージ等を含むデバイス終端構造周辺のdV/dtロバスト性やラッチアップ耐性等を調べる信頼性試験が行われます。それを規格化した試験がDRB試験になります。

DRB試験の試験条件を表1に示します。

表1 DRB試験(Dynamic Reverse Bias)の試験条件

| 条件項目 | 値 |

| 試験継続時間 | ≥ 1011 サイクル |

| 試験温度 | Tvj ≥ 25 ℃ |

| ドレイン–ソース過電圧 | 0.8 VDS,max ≤ VDS ≤ 0.95 VDS,max |

| ドレイン–ソース直流試験電圧 VDS,DC | > 0.5 VDS,max |

| dVDS/dt ターンオン | ≤ –50 V/ns |

| dVDS/dt ターンオフ | ≥ 50 V/ns |

| スイッチング周波数 | 25 kHz ≤ f ≤ 1 000 kHz |

| 負荷電流 IDS | ≥ 0 A |

| デューティ比 | 40% … 60% |

| “ON” ゲート電圧 VGS,on (アクティブモード) | VGS,on = VGS,on,recom |

| “OFF” ゲート電圧 VGS,off (アクティブ/パッシブ) | VGS,off = VGS,off,recom |

DRB試験の各テスト方式におけるメリット、デメリット

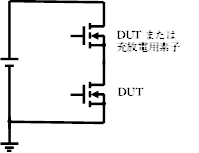

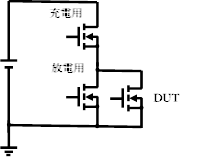

AQG-324で規定されているテスト方式には、①DUT自身でスイッチングし、dV/dtを発生させるパターン(アクティブモード)と、②充放電用の素子をDUTに接続し、DUTはオフしたまま、充放電用の素子をスイッチングさせ、dV/dtを発生させるパターン(パッシブモード)の2種類があり、それぞれの試験回路概略図とメリット、デメリットを表2に示しますのでご参考にしてください。

表2 dV/dt試験の試験回路例比較

| DUT自身でスイッチングする場合 (アクティブモード) |

充放電用素子でスイッチングする場合 (パッシブモード) |

|

| 試験回路例 |  |

|

| 回路動作 | DUTや充放電用素子を交互にスイッチング させることでdV/dtを印加 |

充放電用素子を交互にスイッチングさせる ことでdV/dtを印加(DUT自身はオフのまま) |

| メリット | ・両方DUTにすることで試験台数を2台に 増やせる。 ・回路がシンプルなため、回路規模を小さく でき、回路インダクタンスも小さい。 |

・充放電用素子の自由度が高いため、dV/dt を大きくしやすい。 ・充放電用素子でスイッチングするため、高 速で動作させてもDUTのゲートに過剰なス トレスが加わらない。 ・主に充放電用素子が発熱するため、DUTの 温度管理は比較的簡単になる。 |

| デメリット | ・DUT自身でスイッチングさせるため、高速 で動作させる場合はゲートに過剰なストレ スが加わらないか注意する必要がある。 ・DUTが発熱するため、放熱や温度調整が 必要になる。 ・両方DUTにすると個別に速度調整ができ なくなる。 |

・試験回路の規模が大きく、回路インダクタ ンスも大きくなる。 ・試験台数は1台のみであり、大量に試験す る場合は不向きである。 |

DRB試験の高dV/dtを実現するためのコツ

AQG-324規格の試験条件にdV/dT>50V/nsの規定があります。デバイスにもよりますが、高dV/dtを実現するにはある程度工夫が必要になってきます。以下に注意すべき点を挙げます。

- 可能な限り回路インダクタンスを小さくする。

- 使用するスイッチ用デバイスはできるだけ高速なものを使用する。

- ゲートドライバは駆動能力が高く、立ち上がりが高速なものを使用する。

まず1番目ですが、可能な限り回路インダクタンスを小さくする必要があります。例えばCoss=1nFとした場合、dV/dt=50V/nsであれば瞬時ですが、50Aの変位電流が流れることになります。したがって、dI/dtも大きくなり、回路インダクタンスが数nHでも電圧降下が大きくなり、スイッチング速度が低下します。デバイスのパッケージは表面実装型のものを使用する、回路のループは極力小さくする等、回路インダクタンスを1nHでも小さくするべきです。

次に2番目について、使用するスイッチ用デバイスはできるだけ高速なものを使用することが必要です。チップ面積が小さいほどデバイスの容量自体も小さくなるため、チップサイズが小さい方が有利になります。ただし、小さすぎると変位電流を流しきれなくなるため、その点は注意する必要があります。また、チップサイズが小さいデバイスは内蔵のゲート抵抗が大きく設計されている場合がありますので、その点も注意する必要があります。

最後に、ゲートドライバは駆動能力が高く、立ち上がりが高速なものを使用する必要があります。スイッチングは非常に速いため、単純に駆動電流が大きいだけではなく、高速で立ち上がることも求められます。また、ゲートまでの配線は極力短くし、可能な限りインダクタンスを低減する必要があります。

以上が高dV/dtを実現するための主なコツになります。

当社では様々なデバイスに応じた試験が可能ですので、お気軽にご相談ください。

最後までお読みいただき、ありがとうございます。

<関連リンク>

【採用】

【関連リンク】

WTIブログもご覧ください

【関連ブログ】

- パワーエレクトロニクスって、どういうもの?

- 「パワー半導体」の信頼性試験について

- ダイオードのせん頭サージ電流(IFSM)とは

- 「パワー半導体」のスイッチング評価は難しい? ~その1~

- 「パワー半導体」のスイッチング評価は難しい? ~その2~

- パワーMOSFETのアバランシェ試験とは ~その1~

- パワーMOSFETのアバランシェ試験とは ~その2~

- パワーMOSFETのアバランシェ試験とは ~その3~

- パワーデバイスの短絡試験について

- 「パワー半導体」スイッチング評価の電流測定

- 「パワーデバイスの基礎講座」のご紹介

- CMOS[低耐圧MOSFET]とパワー半導体との違い

- パワー半導体の評価は安全が第一

- SiCデバイスを使って電源を高効率化してみました

- 電源設計技術者が見つからない時代 だから自社で育成する!

- いまさらなんですが、SiCって何がいいのでしょうか?

- DGS試験とは? ~次世代パワー半導体(SiC)のストレス試験~

- AQG 324が4年ぶりの更新!DGS試験はどうなった

- AC-BTI (GSS/DGS) 試験とは?

- 車載用電子部品の規格に準拠した試験サービス立ち上げに向けて

- AEC準拠試験に「計測評価プラットフォーム」を活用♪