みなさん、はじめまして。

みなさん、はじめまして。

パワー設計課パワー設計第一ユニットの岡田です。どうぞよろしくお願いします。

パワー設計課では、さまざまなパワー半導体製品の開発に関わっています。

(パワーモジュール評価サービスはこちら)

パワー半導体は、さまざまな用途のスイッチング素子として使用されており、大きな電圧や電流を扱うのが特徴です(電圧では数100 Vから数kV程度まで、電流では数10Aから数100A程度まで)。

私はキャリア採用にて当社に入社しました。

前職では、さまざまな半導体製品に搭載されるA/DコンバータやD/Aコンバータなどを開発しており、主にコンバータ回路の構成要素であるオペアンプ、コンパレータ、バイアス回路、などのCMOSアナログ回路設計を行っていましたが、入社後に配属されたパワー設計課で扱うパワー半導体は、初めて扱う素子であり知識もありませんでした。

このため、社内の技術教育センターのパワーエレクトロニクス講座を受講して、パワーデバイスの基本機能と動作原理、パワーモジュールを使った応用製品(スイッチングレギュレータ、インバータ)の基礎理論を学びました。講座を通じて、同じ半導体でもCMOSとパワー半導体とでは様々な違いがあることを学んだので簡単に紹介します。

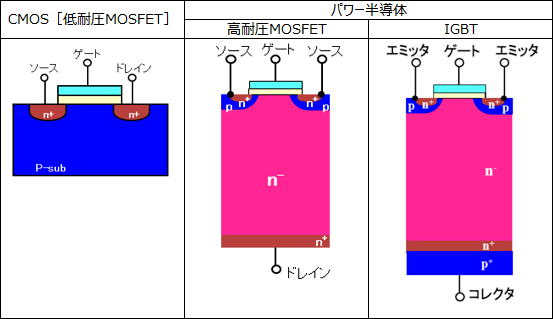

CMOSなどで用いられる低耐圧MOSFET(図1ではNch MOSFETのみ示しています)とパワー半導体[高耐圧MOSFET、IGBT]のデバイス構造の比較を図1に示します。

図1 低耐圧MOSFETとパワー半導体のデバイス構造比較

CMOSはウエハ表面のみを使用し、高速動作、低消費電力、小面積、をターゲットとして開発しますが、パワー半導体では、ウエハの表面から底面までを使用して、縦方向に大電流を流すことで高耐圧化を実現していることにまず違いを感じました。

IGBTは、高耐圧型MOSFETのドレイン側にp+層を追加することで、MOSFETとバイポーラトランジスタの複合素子のデバイス構造となっています。バイポーラの特徴も併せ持つことで、耐圧を高めつつ、導通損失を小さくしている、ということを理解しました。

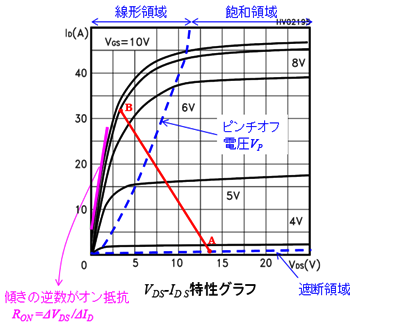

図2は、高耐圧MOSFETのVDS-IDS特性を、VGS=0Vから10Vまで振ってプロットしたグラフです。

図2 高耐圧MOSFETのVDS-IDS特性

CMOSでのオペアンプやバイアス回路の設計では、安定動作を必要とするため、VDSが大きい飽和領域を使用し、なるべく消費電力を小さくするため、VGSを小さく設計します。

一方、パワー半導体では、スイッチングによる損失を小さくするため、VDSが小さい線形領域を使用し、オン抵抗による損失を小さくするため、VGSをなるべく大きく設定するので、ここの考え方が真逆となっています。

また、CMOSは1~3V程度の電源電圧で動作しますが、パワー半導体では大電力を扱うので、実験評価を行う際に、感電防止対策をきっちり行わなければなりません。低消費電力・低電圧動作を追求するCMOS回路出身の私には、安全対策をして業務に臨むというのは、非常に新鮮な経験でした。

以上、私が転職を通じて新たに出会ったパワー半導体とCMOS[低耐圧MOSFET]の違いについて、簡単ですがご紹介させていただきました。

当社では、募集技術に対して未経験の方や経験が浅い方であっても、社内の技術教育センターの教育プログラムを通じて、業務に従事できるレベルまで指導を受けることができます。私もこのプログラムを活用してこれまでの経験を活かしながら、新たな経験を積むことができました。

【関連リンク】

社内教育のご紹介

WTI技術講座は足掛け9年の実績です

中途採用

「教育」が、設計/開発会社を選択するときの重要判断ポイント

男性初の育児休暇を半年間とりました!

WTIメールマガジンの配信(無料)

WTIエンジニアが携わる技術内容や日々の業務に関わる情報などを毎週お届けしているブログ記事は、メールマガジンでも購読できます。ブログのサンプル記事はこちら

WTIメールマガジンの登録・メールアドレス変更・配信停止はこちら

WTIの技術、設備、設計/開発会社の使い方、採用関連など、幅広い内容を動画で解説しています。